# CESSION CONTRACTOR OF CONTRACT

### Methods measure power electronics' efficiency

Liping Zheng, Calnetix, Yorba Linda, CA

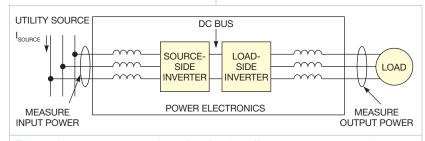

Validating the sytem efficiency of a power-electronics circuit is essential in evaluating the overall system performance, design optimization, and sizing of cooling systems. Figure 1 shows the conventional method of performing efficiency measurement. The powerelectronics system operates at the rated output-power level, and, by measuring the input power and output power, you can calculate the system's efficiency using the equation  $\eta = (P_{OUT}/P_{IN}) \times 100\%$ , where  $P_{OUT}$  is output power and  $P_{IN}$  is input power. In other words, the measured input power is equal to the output power plus the power loss of the system.

However, measuring the efficiency of a high-power system that delivers power to loads such as motors, generators, or industrial-computer equipment requires a source that delivers the rated power. The infrastructue therefore should comprise a suitably rated source and an equivalent load that can support the rating of the power-electronics system you are evaluating. These requirements can drive up the facility's infrastructure cost; for one-time design-validation measurements, this cost is difficult to justify.

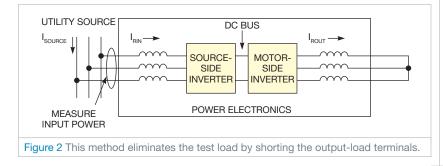

This Design Idea describes alternative methods of measuring the efficiency of a high-power power-electronics system that simplifies the test-infrastructure requirement by eliminating the test load and using a source that must support only the loss of the power-electronics system. **Figure 2** shows the proposed method, which eliminates the test load by shorting the output/load terminals. The sys-

Figure 1 In a conventional method of performing efficiency measurement, the power-electronics system operates at the rated output-power level.

#### DIs Inside

42 Circuit extends battery life

44 Pulse generator corrects itself

46 Reflective object sensor works in bright areas

► To see all of *EDN*'s Design Ideas, visit www.edn.com/design ideas.

tem's control algorithm maintains the required input- and output-current amplitude and frequency by developing circulating reactive power. IGBTs (insulated-gate bipolar transistors) and magnetic components dominate the system's losses, which are functions of the amplitude and frequency of the input and output currents. The loss is also less sensitive to the power-factor and PWM (pulse-width-modulation) index.

To know the required input and output current, you must estimate the system's power factor, the motor's back EMF (electromotive force), and the systems's source voltage. This example uses a field-oriented control for both sourceand load-side inverters, resulting in the following **equations**:

$$\begin{split} I_{\text{ROUT}} &= I_{\text{ROUT\_RE}} + j I_{\text{ROUT\_IM}} = \frac{P_{\text{OUT}}}{\sqrt{3} V_{\text{BEMF}}}; \\ I_{\text{RIN}} &= I_{\text{RIN\_RE}} + j I_{\text{RIN\_IM}} = \\ &\frac{P_{\text{RIN}}}{\sqrt{3} V_{\text{GRID}}} = \frac{P_{\text{OUT}} / \eta_{\text{E}}}{\sqrt{3} V_{\text{GRID}}}, \end{split}$$

where  $I_{ROUT}$  is the required output current, which comprises real current,  $I_{ROUT\_RE}$ , and reactive current,  $I_{ROUT\_IM}$ ;  $I_{RIN}$  is the required input current, which comprises the real current,  $I_{IN\_RE}$ , and the reactive current,  $I_{IN\_IM}$ ;  $P_{RIN}$  is the

## designideas

required input power;  $P_{OUT}$  is the output power at the test condition;  $V_{\text{BEMF}}$  is the motor's back EMF;  $V_{GRID}$  is the grid voltage; and  $\eta_{\text{E}}$  is the estimated efficiency of the circuit.

By maintaining the input current to be  $I_{RIN}$  and the output current to be  $I_{ROUP}$  the measured input real power will be close to the power loss,  $P_{LOSS}$ , at the

actual output-power level,  $P_{OUT}$  Therefore, you can calculate the efficiency as follows:  $\eta = (P_{OUT})/(P_{OUT} + P_{LOSS}) \times 100\%$ .

If the measured efficiency, which you calculate using this **equation**, does not quite match the estimated efficiency,  $\eta_{\rm E}$ , update the second **equation** using the measured efficiency,  $\eta$ , and repeat the measurement until they are close. Cal-

netix (www.calnetix.com) has used this method to evaluate the efficiency of a 125-kW power-electronics system, compared the results with the conventional measurements, and found them to be closely matching.

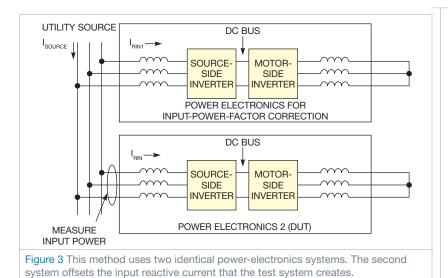

Most high-power power-electronics systems have high efficiency, which means that the real current is much less than the reactive current. To reduce the required current from the grid, you can use the method in Figure 3, which uses another identical system to offset the input reactive current that the test system creates. By providing a path for circulating reactive power, the utility sources the lost power only, not the total power. In Figure 3, the input current of the second power-electronics circuit is  $I_{RIN}$ =  $I_{RIN_{RI}}$ +j $I_{RIN_{IM}}$ . By setting the first circuit to have an input current of  $I_{RIN1} \approx I_{RIN_RE}$ jI<sub>RIN\_IM</sub>, the power from the source is only  $I_{\text{SOURCE}} = I_{\text{RIN}1} + I_{\text{RIN}} \approx I_{\text{RIN} \text{RE}} + I_{\text{RIN} \text{RE}} + I_{\text{II}} = j(I_{\text{RIN} \text{IM}} - I_{\text{RIN} \text{IM}}) = 2I_{\text{RIN} \text{RE}}$ . The circuit uses the input current from the source only to overcome the power losses of the two circuits, thereby eliminating the need for a high-power infrastructure.EDN

#### Circuit extends battery life

José M Espí, Rafael García-Gil, and Jaime Castelló, University of Valencia, Valencia, Spain

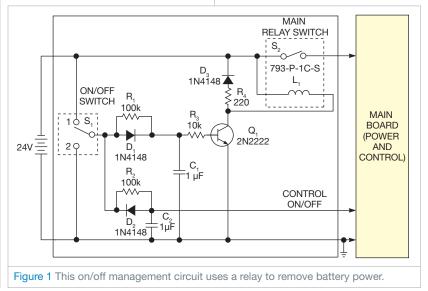

Two previous Design Ideas describe simple ways to automatically disconnect a battery from its load after a preset on period, which extends battery life (references 1 and 2). These circuits have little loss in standby operation, but they do draw some current. The circuit in this Design Idea presents a simpler way to perform the same function with fewer components and with no power consumption during standby operation (Figure 1). Moreover, the network comprising  $R_2$ ,  $D_2$ , and  $C_2$  activates and deactivates the circuit. An additional control signal, control on/off, becomes slower than the battery's on/ off cycle.

Switching  $S_1$  to Position 1, the on position, the 24V battery quickly charges capacitor  $C_1$  through diode  $D_1$ . That voltage drives transistor  $Q_1$  into saturation.  $Q_1$ 's saturation magnetizes and activates relay coil  $L_1$ ,

connecting the battery to the main power and control board. Meanwhile, capacitor  $C_2$  charges more slowly through 100-k $\Omega$  resistor  $R_2$ , thus generating the control on/off signal with some delay relative to the relay coil's closing. That scenario occurs after

## designideas

the proper power supply to the power stage and control circuits.

Switching  $S_1$  to Position 2, the off position, causes capacitor  $C_1$  to slowly discharge through resistor  $R_1$  when diode  $D_1$  is off. That action delays  $Q_1$ 's turn-off. Before  $Q_1$  turns off,  $C_2$  quickly discharges through  $D_2$ , indicating that the control should shut down the power. The relay switches off with minimum current. Once  $Q_1$  is off, the relay coil demagnetizes through  $R_4$  and  $D_3$ . The relay switches off, disconnecting the main power and control board from the battery. During this off state, current flows neither in the on/ off circuit of the management board nor to the main board.EDN

#### REFERENCES

Gimenez, Miguel, "Scheme provides automatic power-off for batteries," *EDN*, May 13, 2004, pg 92, http://bit.ly/ aUdD3s.

Xia, Yongping, "Battery automatic power-off has simpler design," *EDN*, March 31, 2005, pg 80, http://bit.ly/ bLJNgb.

#### Pulse generator corrects itself

Marián Štofka, Slovak University of Technology, Bratislava, Slovakia

Using a shift register with parallel output is a common way to design a pulse generator with N inputs and pulsed outputs having a width of T/N. To keep the output pulses consecutive, you can use feedback from the last output to the first input. At power-on, such a circuit can have a random combination of logic zeros and ones, forming an undesired data content of the shift register. To avoid circulating undesired states and to enter a proper sequence, you need a special feedback.

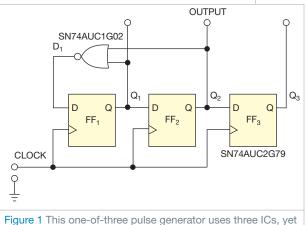

The circuit in **Figure 1** is a three-stage shift register that uses D-type flip-flops. It has three outputs,  $Q_1$ ,  $Q_2$ , and  $Q_3$ , each of which produces a periodic pulse having a width of  $T_{REP}/3$ .  $T_{REP}=3T_{CLK}$  is the period at which the sequence repeats at any of the three outputs. A two-input NOR gate creates the feedback. The gate's D<sub>1</sub> output connects to the D input of flip-flop FF<sub>1</sub>, and its inputs connect to  $Q_1$  and  $Q_2$ . A logic-one bit at D<sub>1</sub> means that, at the nearest low-to-high transition of the clock, this signal will place a logic one at output Q<sub>1</sub>.

You can interpret this feedback in words by writing a logic zero into  $FF_1$ at the nearest low-to-high transition of the clock signal, if at least one of the  $Q_1$  or  $Q_2$  outputs has a logic-one state. You write a logic one into  $FF_1$  if both the  $Q_1$  and the  $Q_2$  outputs are at logic zero. This feedback adds a self-correcting feature, which is illustrated by

it avoids false logic states.

the assumption that the initial state of the circuit is intentionally undesired.

Using this result, the following sequences illustrate state correction, in which the logical states in the bit triads correspond left to right to  $Q_1$ ,  $Q_2$ , and  $Q_3$ :

$$111 \rightarrow 011 \rightarrow 001 \rightarrow 100 \rightarrow 010 \rightarrow 001$$

$000 \rightarrow 100 \rightarrow 010 \rightarrow 001$

From this example, you can see that erroneous state 111 self-corrects within

two periods of the clock. For the undesired 000 state, the proper cycling enters at the nearest low-to-high transition of the clock signal.

You can determine the upper limit of the clock frequency from an assumption of the gate output, which changes after a low-to-high transition of the clock. This condition must be ready

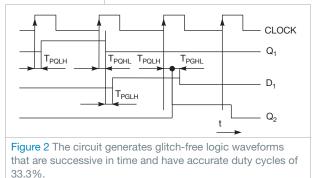

with a setup time,  $T_{\text{SETUP}}$ , the next time the clock transitions from low to high (Figure 2). Thus, T<sub>CLKMIN</sub>=  $T_{PQHL} + T_{PGLH} + T_{SETUP}$ , where  $T_{PQHL}$  and  $T_{PGLH}$  are signal-propagation delays of the flip-flop and the gate, respectively, at the respective output-level transition. By using the worst-case values of propagation delays from the devices' data sheets, you get a minimum clock period of 4.4 nsec for a supply voltage of 1.8V and a minimum clock period of 3.5 nsec for a supply voltage of 2.5V. As

the 3.5-nsec value gives a clock frequency higher than the guaranteed toggle frequency for the flip-flop, you should accept the maximum clock frequency at 275 MHz for a supply voltage of 2.5V. For a supply voltage of 1.8V, the maximum clock frequency should be 227 MHz. The maximum repetition rate of signals at  $Q_1$ ,  $Q_2$ , and  $Q_3$  outputs is the maximum clock frequency divided by three, or 75.6 MHz.EDN

# designideas

# Reflective object sensor works in bright areas

Vladimir Rentyuk, Modul-98 Ltd, Zaporozhye, Ukraine

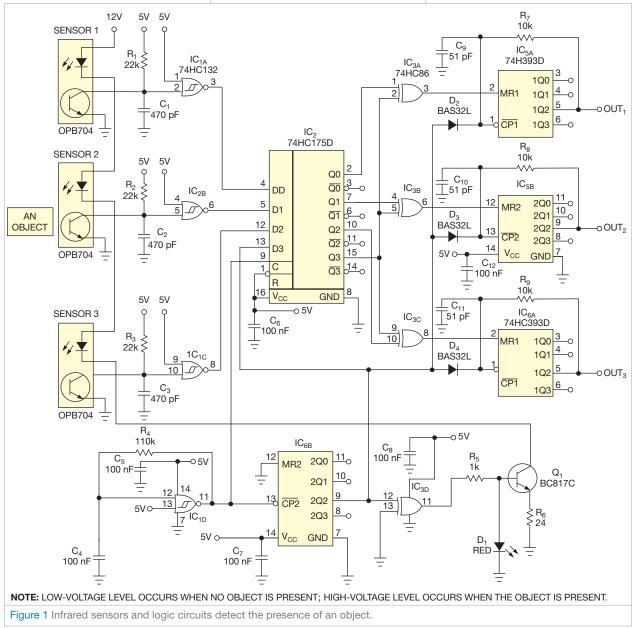

When using a reflective object sensor, counting and identifying objects is sometimes difficult in the presence of electrical noise or bright ambient light. The circuit in **Figure 1** shows an inexpensive solution to this problem using three independent and simultaneously working reflective object sensors. The circuit is suitable for many types of objects, but it targets use with objects such as cards.

The circuit uses three OPB704 reflective optical sensors with Schmitt-trigger NAND comparators  $IC_{1A}$ ,  $IC_{1B}$ , and  $IC_{1C}$  on each output.  $IC_{1D}$  functions as a clock generator, and counter  $IC_{6B}$  functions as a divide-by-eight counter that divides the clock frequency. That signal drives

$IC_{4D}$ , which acts as a buffer to drive transistor  $Q_1$ .

To understand how the circuit works, consider Sensor 2.  $IC_{1B}$ 's output will be low if the sensor's phototransistor doesn't detect IR rays reflected from an object. Both of  $IC_{1B}$ 's inputs are high; therefore, the D1 input of  $IC_2$  is low. In any case, if the sensor's phototransistor detects IR rays reflected from an object, the D1 input of  $IC_2$  is high. The level corresponding to the current situation transfers through  $IC_2$ 's  $Q_1$  output (Pin 7) by a write signal on the C input (Pin 9). The write signal is a leading edge of puls-

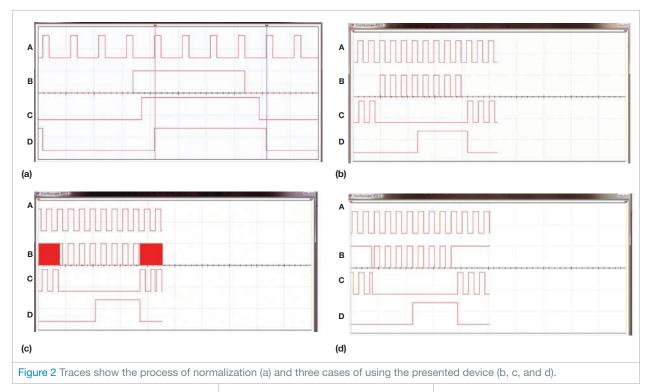

es from the clock generator. The signal from divider  $IC_{6B}$  becomes the D3 input of  $IC_2$ . A level of the divided clock signal transfers to  $IC_2$ 's Q3 output (Pin 15) upon receiving a write signal from the C input (Pin 9). The signals on the Q1 and Q3 outputs have equal duration except when the sensor's phototransistor detects IR rays reflected from an object. Figure 2a shows the process of this normalization. Exclusive-OR gate  $IC_{3B}$  compares the Q1 and Q3 outputs from IC<sub>2</sub>. If they have the same logic level and duration, then  $IC_{3B}$ 's Pin 6 is low, and  $IC_{3B}$  generates pulse signals. If signals from outputs Q1 and Q3 on IC, are unequal, you must reset counter  $IC_{5B}^{2}$ 's reset signal, and its output 2Q2 at OUT<sub>2</sub> is low. The Q2 outputs of counters  $IC_{5A}^{-}$ ,  $IC_{5B}^{-}$ , and  $IC_{6A}^{-}$  are low whenever the input signals of comparator circuits  $IC_{3A}$ ,  $IC_{3B}$ , and  $IC_{3C}$  are unequal. This situation occurs if Sensor 2 doesn't detect an object or receive any external signals-for example, IR noise from fluorescent lamps or interfering ambient light, alternating light, or flashes.

The outputs of  $IC_{3A}$ ,  $IC_{3B}$ , and  $IC_{3C}$ are equal only when all phototransistors detect a signal from their respective IR emitting diodes—that is, when a card is presented in front of Sensor 2 (**Figure 2b**). You must choose a clock

frequency with regard to a delay time of the system. A leading edge triggers IC<sub>2</sub>, a 74HC175, and a falling edge triggers  $IC_{6B}$ , a 74HC393. Because of the counters, this system automatically adjusts itself after any changes of frequency in its clock generator. Thus, if counter  $IC_{5B}$ does not have a reset signal during a period equal to four periods of a reference signal, its output (Pin 9) is high, and the counter latches through  $\rm R_8^{}.$  The logic-high level appears on  $\rm OUT_2$  until you remove the card. In this case, the detected inequality signal from the sensor with the reference signal and the counter, IC<sub>5B</sub>, causes a reset signal. Figures 2b, 2c, and 2d show three cases of using the presented device.

**Figure 2b** shows a case of normal operation. You can see the results of comparing a reference signal (Trace C) and a signal of  $IC_{1B}$ 's output (Trace D). The signal of  $IC_{1B}$ 's output (Trace B) is low when no card appears. When the card enters the zone of vision of a sensor (Trace B), it is a sequence of normalized pulses. The output of the device at Pin 9 of  $IC_{5B}$  (Trace D) changes its level from low to high after four cycles of both signals, but it will immediately change to low if you remove the card.

Figure 2c shows operation of the de-

vice under strong IR noise. The signal of  $IC_{1B}$ 's output (Trace B) contains some high-frequency signals if a card isn't present and is a sequence of normalized pulses when a card is present. The output of the device at Pin 9 of  $IC_{5B}$  (Trace D) indicates the presence of a card by changing its level from low to high after four cycles of these signals. It immediately changes to low if you remove the card from the zone.

**Figure 2d** shows operation of the device under ambient direct lighting. You can see the results of comparing signals. In this case, the signal at  $IC_{1B}$ 's output (Trace B) is constant high when a card isn't present. When the card enters a sensor's zone of vision (Trace B), the signal is a sequence of normalized pulses. The output of the device at Pin 9 of  $IC_{5B}$  (Trace D) indicates this condition by changing its level from low to high after four cycles of both signals. It immediately changes from high to low when you remove the card from the zone.

Capacitors  $C_1$ ,  $C_2$ , and  $C_3$  are optional. They protect input circuits from electromagnetic noise when, for example, long wires connect the sensors and the device. Capacitors  $C_9$ ,  $C_{10}$ , and  $C_{11}$  provide performance reliability by protecting the counters from short pulses.EDN